3Dフラッシュメモリ「BiCS FLASH™」の誕生

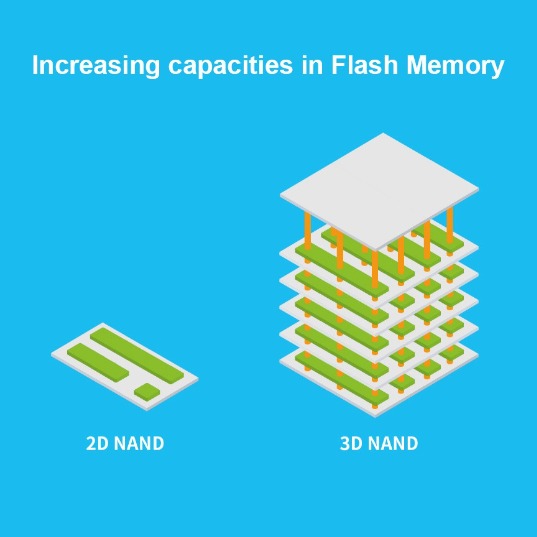

Kioxia の前身である東芝は、1987年に NAND型フラッシュメモリの開発に成功し、1991年には世界で初めて量産を開始しました。設計ガイドラインとプロセスの進化を通じて、NAND フラッシュメモリの容量は継続的に向上してきました。しかし、平面プロセスの制約内で容量を増加させることは非常に困難になっていました。このメモリ容量不足の課題に対処するため、Kioxia は新しい技術を採用してフラッシュメモリセルを垂直に積層し、2007年に 3D フラッシュメモリ積層技術を発表しました。その基盤の上に、Kioxia はさらに関連技術を発展させ、3D フラッシュメモリ「BiCS FLASH™」を導入しました。

BiCS FLASH™ テクノロジー

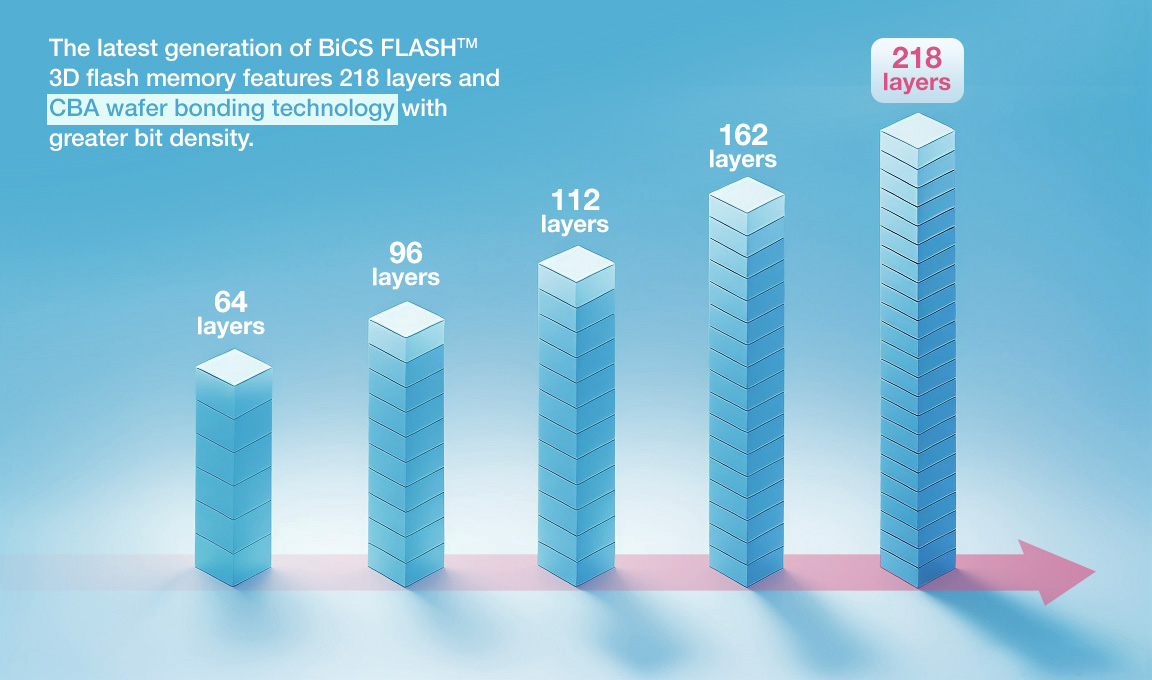

3D NAND の垂直積層方式から始まり、技術の進化とともに積層数は増加してきました。

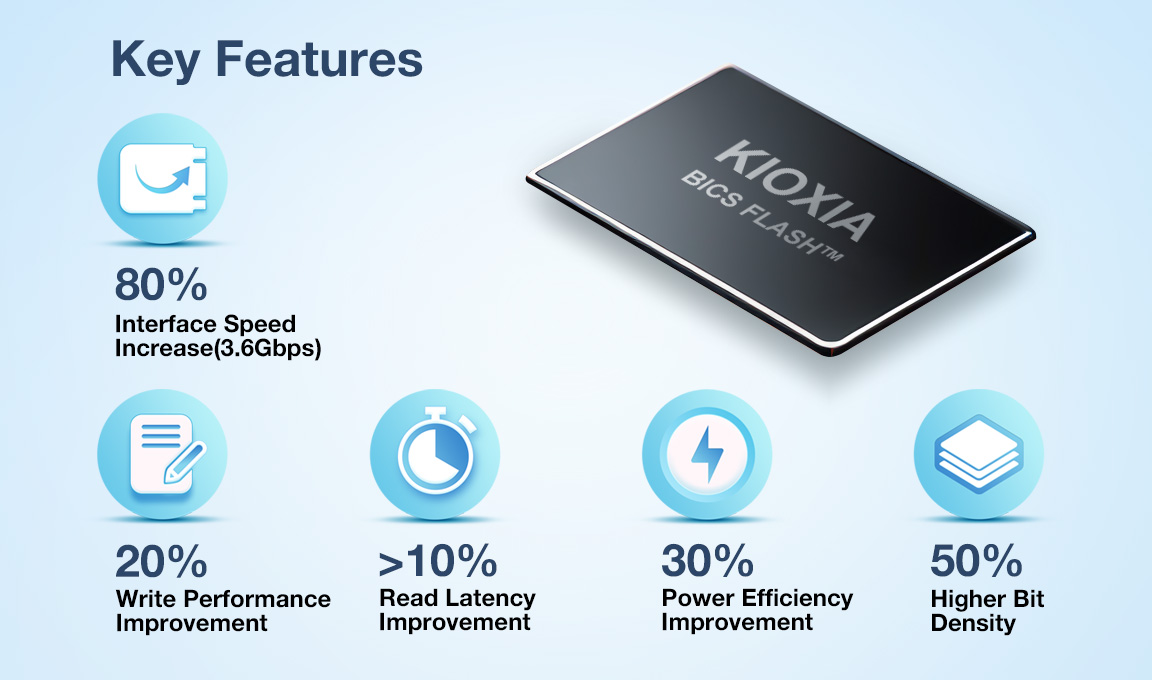

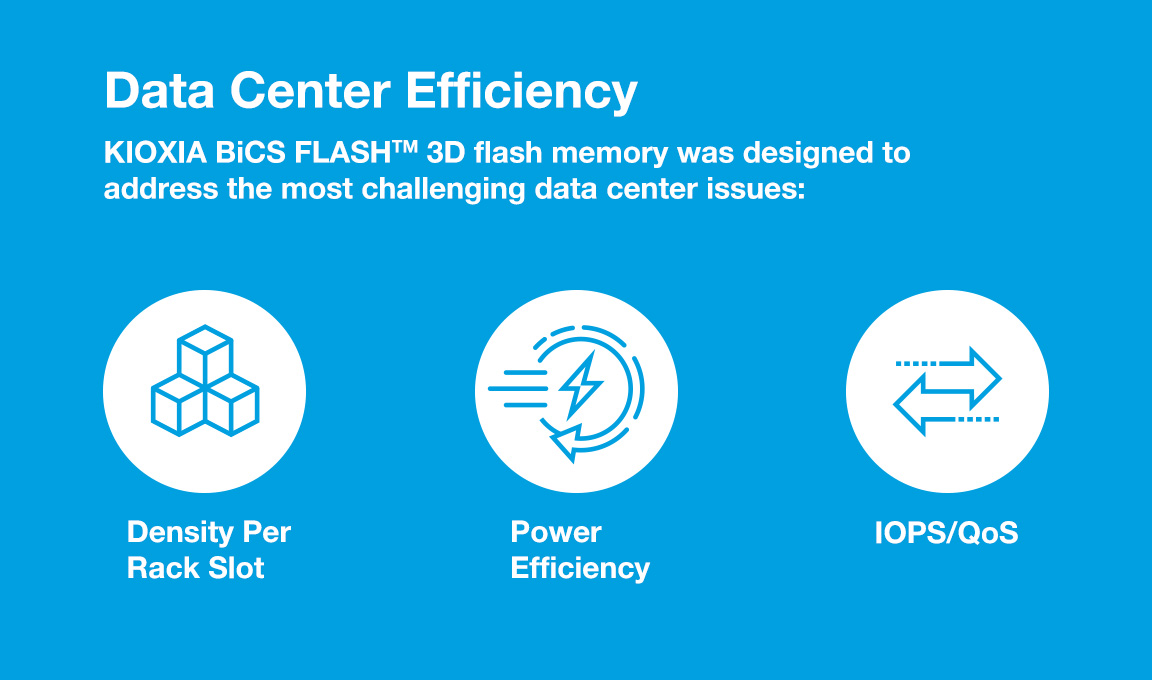

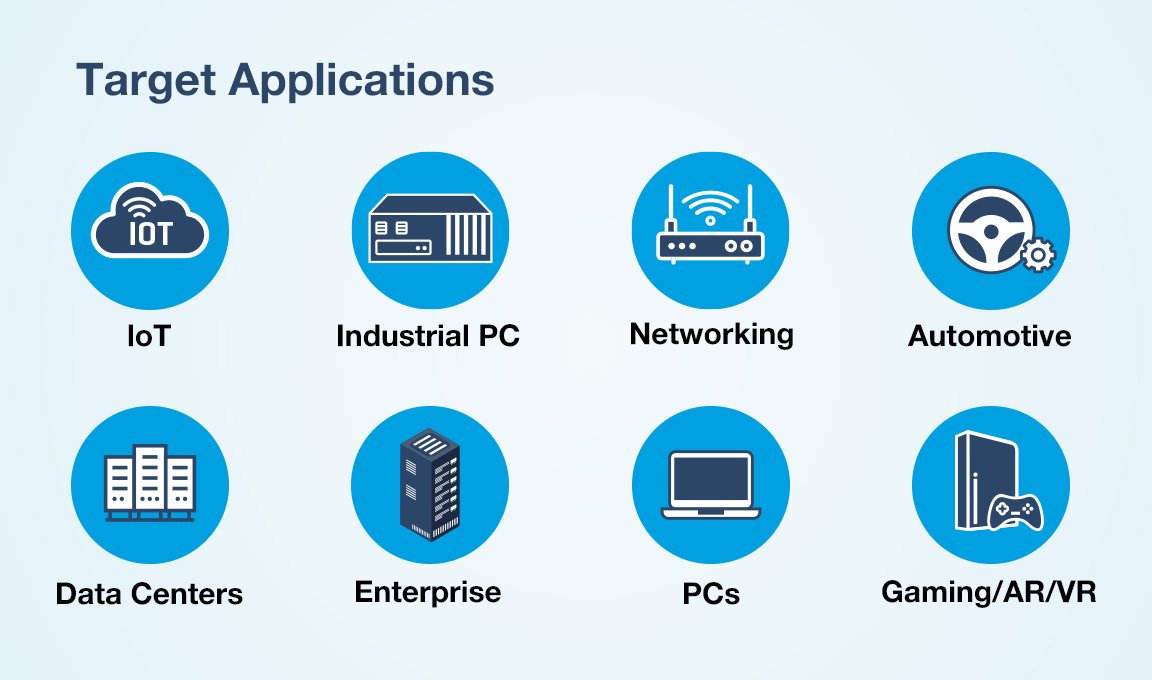

第8世代の KIOXIA BiCS FLASH™ 3Dフラッシュメモリ は、218層と CMOS Directly Bonded to Array (CBA) ウェーハ接合技術を特徴とし、高度なスマートフォン、PC、SSD、データセンターなどのデータ中心アプリケーションのニーズに応えるアーキテクチャ革新を実現しました。性能、高密度、コスト効率が求められる場合に、BiCS FLASH™ 3Dフラッシュメモリは最適なソリューションを提供します。

技術が成熟するにつれて、各 NAND の単価は低下し、単位あたりの記憶容量は増加し、コスト効率が最適化されています。

KIOXIA BiCS FLASH第8世代

主な特長

2D NAND は限られた平面上にセルを追加する方式ですが、需要と技術の進化に伴い、平面配置可能なセル数には限界があります。この技術的進化により 3D NAND が誕生しました。新しい 3D NAND 技術は 2D NAND を基盤としつつ、平面から立体構造へ移行しました。これにより、BiCS FLASH™ セルを積層できる空間が大幅に増加し、記憶容量が大きく拡張されます。

高速書き込み性能

3D 積層構造により、セル間の距離が 2D NAND よりも大幅に拡大します。これによりメモリセルのばらつきが軽減され、各書き込みシーケンスのデータ解釈が高速化され、書き込み速度が向上します。

2D NAND の微細化に伴う信頼性問題に比べ、3D NAND の垂直積層技術はセル間の距離を拡大させ、セル間干渉を軽減し、安定性を向上させます。

低消費電力

BiCS FLASH™ は書き込みシーケンスあたりのデータ量を増加させ、処理速度を向上させます。これにより、2D NAND と比較してデータ処理に必要な電力を大幅に削減し、省エネルギーを実現します。

__24G16fLAYD.png)

__24G16MPGSr.png)

__24G16aLuso.jpg)

__24G16W17nI.png)

__24G16TJahh.png)